JEDEC Plans LPDDR6-Based CAMM, DDR5 MRDIMM Specifications

by Anton Shilov on July 23, 2024 7:00 PM EST

Following a relative lull in the desktop memory industry in the previous decade, the past few years have seen a flurry of new memory standards and form factors enter development. Joining the traditional DIMM/SO-DIMM form factors, we've seen the introduction of space-efficient DDR5 CAMM2s, their LPDDR5-based counterpart the LPCAMM2, and the high-clockspeed optimized CUDIMM. But JEDEC, the industry organization behind these efforts, is not done there. In a press release sent out at the start of the week, the group announced that it is working on standards for DDR5 Multiplexed Rank DIMMs (MRDIMM) for servers, as well as an updated LPCAMM standard to go with next-generation LPDDR6 memory.

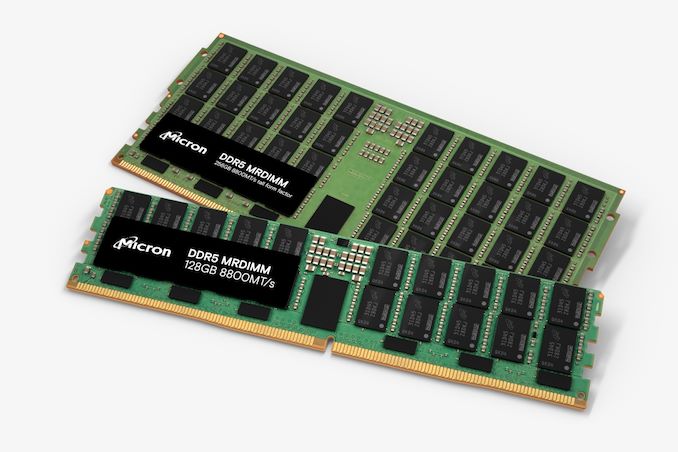

Just last week Micron introduced the industry's first DDR5 MRDIMMs, which are timed to launch alongside Intel's Xeon 6 server platforms. But while Intel and its partners are moving full steam ahead on MRDIMMs, the MRDIMM specification has not been fully ratified by JEDEC itself. All told, it's not unusual to see Intel pushing the envelope here on new memory technologies (the company is big enough to bootstrap its own ecosystem). But as MRDIMMs are ultimately meant to be more than just a tool for Intel, a proper industry standard is still needed – even if that takes a bit longer.

Under the hood, MRDIMMs continue to use DDR5 components, form-factor, pinout, SPD, power management ICs (PMICs), and thermal sensors. The major change with the technology is the introduction of multiplexing, which combines multiple data signals over a single channel. The MRDIMM standard also adds RCD/DB logic in a bid to boost performance, increase capacity of memory modules up to 256 GB (for now), shrink latencies, and reduce power consumption of high-end memory subsystems. And, perhaps key to MRDIMM adoption, the standard is being implemented as a backwards-compatible extension to traditional DDR5 RDIMMs, meaning that MRDIMM-capable servers can use either RDIMMs or MRDIMMs, depending on how the operator opts to configure the system.

The MRDIMM standard aims to double the peak bandwidth to 12.8 Gbps, increasing pin speed and supporting more than two ranks. Additionally, a "Tall MRDIMM" form factor is in the works (and pictured above), which is designed to allow for higher capacity DIMMs by providing more area for laying down memory chips. Currently, ultra high capacity DIMMs require using expensive, multi-layer DRAM packages that use through-silicon vias (3DS packaging) to attach the individual DRAM dies; a Tall MRDIMM, on the other hand, can just use a larger number of commodity DRAM chips. Overall, the Tall MRDIMM form factor enables twice the number of DRAM single-die packages on the DIMM.

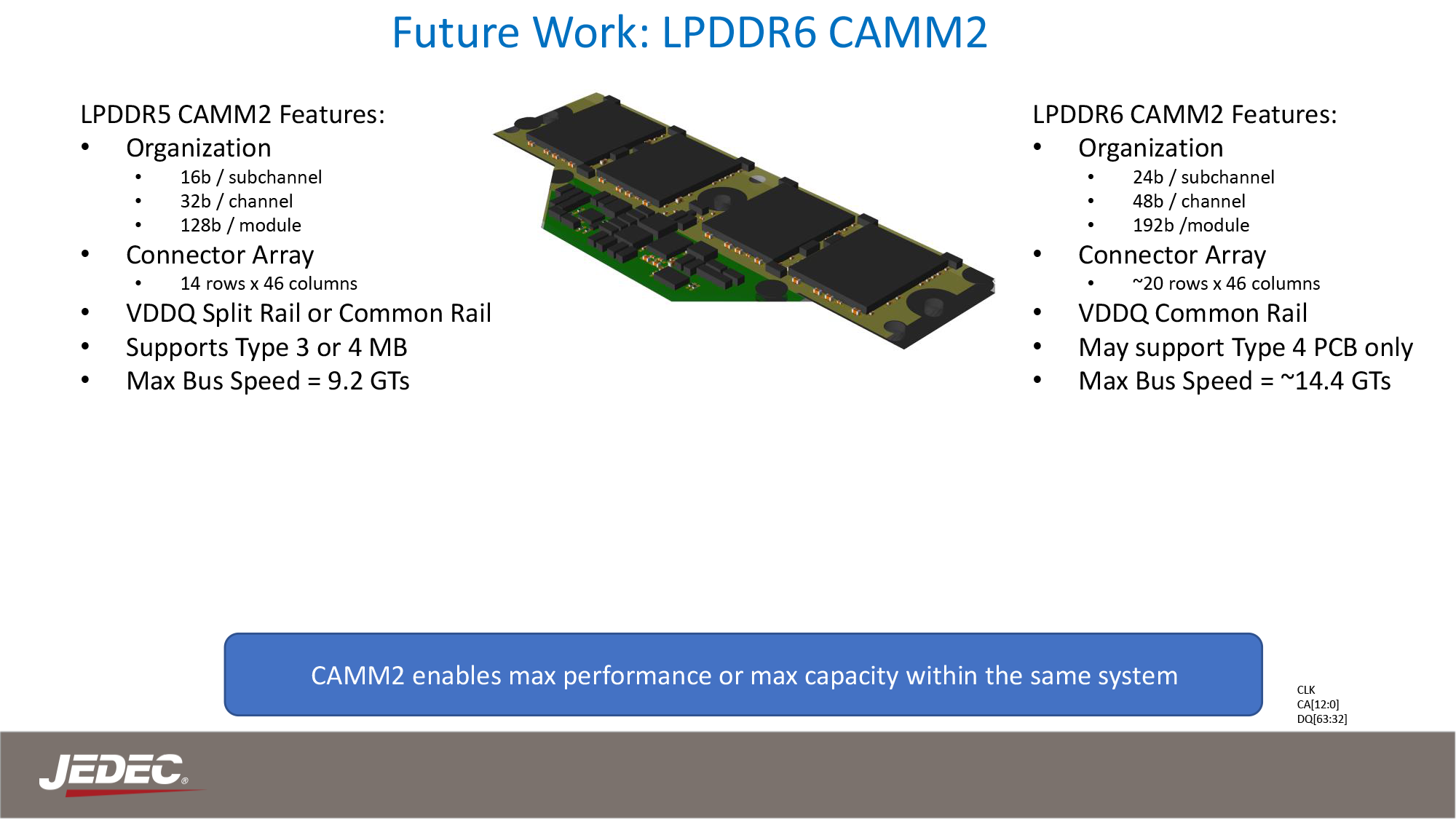

Meanwhile, this week's announcement from JEDEC offers the first significant insight into what to expect from LPDDR6 CAMMs. And despite LPDDR5 CAMMs having barely made it out the door, some significant shifts with LPDDR6 itself means that JEDEC will need to make some major changes to the CAMM standard to accommodate the newer memory type.

JEDEC Presentation: The CAMM2 Journey and Future Potential

Besides the higher memory clockspeeds allowed by LPDDR6 – JEDEC is targeting data transfer rates of 14.4 GT/s and higher – the new memory form-factor will also incorporate an altogether new connector array. This is to accommodate LPDDR6's wider memory bus, which sees the channel width of an individual memory chip grow from 16-bits wide to 24-bits wide. As a result, the current LPCAMM design, which is intended to match the PC standard of a cumulative 128-bit (16x8) design needs to be reconfigured to match LPDDR6's alterations.

Ultimately, JEDEC is targeting a 24-bit subhannel/48-bit channel design, which will result in a 192-bit wide LPCAMM. While the LPCAMM connector itself is set to grow from 14 rows of pins to possibly as high as 20. New memory technologies typically require new DIMMs to begin with, so it's important to clarify that this is not unexpected, but at the end of the day it means that the LPCAMM will be undergoing a bigger generational change than what we usually see.

JEDEC is not saying at this time when they expect either memory module standard to be completed. But with MRDIMMs already shipping for Intel systems – and similar AMD server parts due a bit later this year – the formal version of that standard should be right around the corner. Meanwhile, LPDDR6 CAMMs will be a bit farther out, particularly as the memory standard itself is still under development.

Source: JEDEC

19 Comments

View All Comments

Lodix - Wednesday, July 24, 2024 - link

When is the standard LPDDR6 launching?deil - Wednesday, July 24, 2024 - link

Most likely with zen6 at earliest, so mid-late 2025. Guessing. More data welcome.dotjaz - Wednesday, July 24, 2024 - link

Likely 2025? Did you pull that date from your behind? DDR5 was finalised in 2020, AMD released AM5 more than 2 years later. DDR4 was released in 2014, AM4 followee in 2016, DDR3 was released in 2007, can you guess when AM3 was released? AM2 was the only exception so far, but it was 2006 after the 2003 DDR2 release.There's no way AMD would release anything with DDR6 in 2025, 0%, no dice. Can't be clearer.

AMD isn’t even likely to release AM6 in 2026. There's a very very VERY small chance.

It's all but confirmed AMD would release "AM6" with "Zen7" in late 2027 or 2028.

Rudde - Thursday, July 25, 2024 - link

LPDDR6 is not DDR6. Also, AMD is very unlikely to be the first to implement LPDDR6.boozed - Thursday, August 1, 2024 - link

Do you always talk to people like this or only after you've misunderstood the question?NextGen_Gamer - Wednesday, July 24, 2024 - link

I'm not sure why the people below associate LPDDR6 with AMD's future Zen 6 processors. LPDDR memory is a soldered-down, mobile standard - that comes to desktops really only in the form of mini PCs (NUCs as another term). And although yes, Socket AM5 with its DDR5 memory is here for a while, AMD can obviously create new mobile silicon with an updated LPDDR6 controller at any time. I don't know what is on the roadmap, but a refreshed Strix Point product in 2025, still using Zen 5 and RDNA 3.5, but with a LPDDR6 controller could totally happen. Something like that is not dependent on AMD also releasing Socket AM6/DDR6 on the desktop side.nandnandnand - Wednesday, July 24, 2024 - link

DDR6 spec should be finalized by Q1/Q2 2025. LPDDR6 should be done months sooner than that, probably within 2024:https://www.driverscloud.com/en/news/2322/new-gene...

I would guess 2025 for actual production/launch. You'll definitely hear about it before it happens, like the usual "Samsung makes 24/32 GB LPDDR6 package for smartphones" press release.

Lodix - Friday, July 26, 2024 - link

ThanksRοb - Monday, July 29, 2024 - link

Before the standard is finalized, and it comes to desktop / server, it's expected to come to mobile.Maybe supported by Snapdragon 8 Gen 4 LPDDR6, a weaker rumour is Dimensity 9400.

One source: https://www-ajunews-com.translate.goog/view/202403...

https://www.gizchina.com/2024/03/11/lpddr6-memory-...

erinadreno - Wednesday, July 24, 2024 - link

64 cannot be divide by 24. So if the CPU needs to fetch a word, it has to use 2 channels anyway? What would be the rationale behind that?