TSMC Jumps Into Silicon Photonics, Lays Out Roadmap For 12.8 Tbps COUPE On-Package Interconnect

by Anton Shilov on April 26, 2024 4:00 PM EST

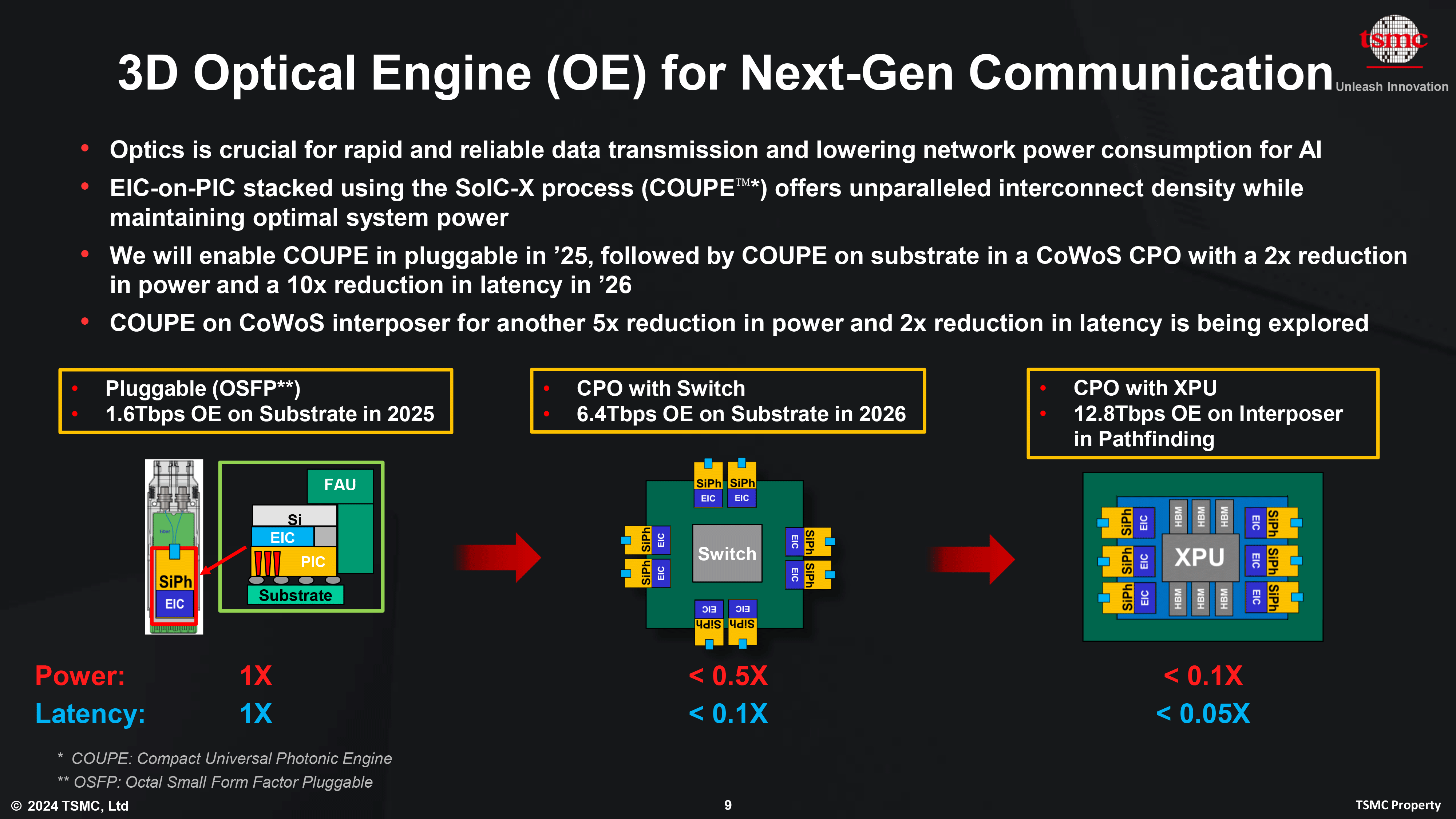

Optical connectivity – and especially silicon photonics – is expected to become a crucial technology to enable connectivity for next-generation datacenters, particularly those designed HPC applications. With ever-increasing bandwidth requirements needed to keep up with (and keep scaling out) system performance, copper signaling alone won't be enough to keep up. To that end, several companies are developing silicon photonics solutions, including fab providers like TSMC, who this week outlined its 3D Optical Engine roadmap as part of its 2024 North American Technology Symposium, laying out its plan to bring up to 12.8 Tbps optical connectivity to TSMC-fabbed processors.

TSMC's Compact Universal Photonic Engine (COUPE) stacks an electronics integrated circuit on photonic integrated circuit (EIC-on-PIC) using the company's SoIC-X packaging technology. The foundry says that usage of its SoIC-X enables the lowest impedance at the die-to-die interface and therefore the highest energy efficiency. The EIC itself is produced at a 65nm-class process technology.

TSMC's 1st Generation 3D Optical Engine (or COUPE) will be integrated into an OSFP pluggable device running at 1.6 Tbps. That's a transfer rate well ahead of current copper Ethernet standards – which top out at 800 Gbps – underscoring the immediate bandwidth advantage of optical interconnects for heavily-networked compute clusters, never mind the expected power savings.

Looking further ahead, the 2nd Generation of COUPE is designed to integrate into CoWoS packaging as co-packaged optics with a switch, allowing optical interconnections to be brought to the motherboard level. This version COUPE will support data transfer rates of up to 6.40 Tbps with reduced latency compared to the first version.

TSMC's third iteration of COUPE – COUPE running on a CoWoS interposer – is projected to improve on things one step further, increasing transfer rates to 12.8 Tbps while bringing optical connectivity even closer to the processor itself. At present, COUPE-on-CoWoS is in the pathfinding stage of development and TSMC does not have a target date set.

Ultimately, unlike many of its industry peers, TSMC has not participated in the silicon photonics market up until now, leaving this to players like GlobalFoundries. But with its 3D Optical Engine Strategy, the company will enter this important market as it looks to make up for lost time.

Related Reading

- TSMC's 1.6nm Technology Announced for Late 2026: A16 with "Super Power Rail" Backside Power

- TSMC 2nm Update: N2 In 2025, N2P Loses Backside Power, and NanoFlex Brings Optimal Cells

- TSMC Preps Cheaper 4nm N4C Process For 2025, Aiming For 8.5% Cost Reduction

- TSMC's System-on-Wafer Platform Goes 3D: CoW-SoW Stacks Up the Chips

9 Comments

View All Comments

watersb - Friday, April 26, 2024 - link

I had no idea this would post today; was thinking about this all day yesterday.Perhaps because I have been piecing together a server from eBay salvage. I have had to deal with pulling the PCIe signaling from the card slots (at the back of the box) to the hot-swap storage backplane (at the front). Re-timers versus re-drivers, or tri-mode host bus adapters, and all these different connectors that the industry thinks are a good idea.

Of course, silicon photonics will usher in a whole new world of connectors and cables.

PicoJoules per bit per second would be nice.

Dante Verizon - Sunday, April 28, 2024 - link

What's the advantage of this? The need to use receivers that convert light back into electrical signals negates the speed advantage of light in communication. lolnandnandnand - Sunday, April 28, 2024 - link

I guarantee these companies would not be bothering with silicon photonics if that was going to be a problem.Terry_Craig - Sunday, April 28, 2024 - link

Well, I wouldn't say that... It's often the case for companies to be drawn to something that seems promising at first glance, only to discover there's a significant caveat. They invest in the hope of resolving the underlying issues, but often find themselves forced to abandon the tech due to either draining their capital or failing to find a viable solution.stephenbrooks - Sunday, April 28, 2024 - link

I believe the losses in copper at high frequencies are the problem. (If you push too much bandwidth, your signal just turns into heat after a few cm in copper). Optic fibres on the other hand largely get rid of that distance-bandwidth tradeoff.mode_13h - Monday, April 29, 2024 - link

I think you're painting with an extremely broad brush, when you say that. By the time someone like TSMC reaches the point of a product announcement, they've done enough R&D to know that the tech solves a real problem for their customers. They wouldn't undertake the costs involved in productizing such tech, unless it did.AI is probably a key driver for this, given that 100 Gbps Ethernet seems to be a popular building block for the switched fabrics linking multiple accelerators. That's what Intel/Habana, Tenstorrent, and Cerebras are all doing, currently.

FreckledTrout - Wednesday, May 1, 2024 - link

It increases the distance of low latency high bandwidth communication. You can connect up servers across a data center with photonics but with electrical signals you can do the rack next to it or maybe two racks over at most.Duncan Macdonald - Sunday, April 28, 2024 - link

The power consumption needs to get well under one pico Joule per bit - with the data rates that TSMC are hoping for (12.8 Tbps) one pJ/bit would imply a power consumption of 12.8 watts in a very tiny space. Cooling such a hotspot would not be trivial.mode_13h - Monday, April 29, 2024 - link

That pJ/b figure should span from end-to-end (i.e. split between Rx and Tx). Given that it's currently implemented in 65 nm technology, it sounds like it might not be as small as you're probably assuming.