Intel to Invest $3.5 Billion USD into Foveros and EMIB Production in Rio Rancho

by Dr. Ian Cutress on May 3, 2021 12:00 PM EST

At a news conference today, Intel has announced that its Rio Rancho campus in New Mexico will be getting an investment of $3.5 billion USD for an expansion of its current state-of-the-art facilities for the company to roll out its new Foveros packaging technology in volume for its own products as well as its customers. This comes on top of the $20 billion USD that Intel has committed to two new fabrication plants in its Ocotillo campus in Arizona for wafer production. In partnership with New Mexico state and local government, the new investment is expected to provide 1000 construction jobs over three years, 700 permanent technical positions at the company, and 3500 ancillary positions in the area when the facility is fully functional.

Modern Processor Manufacturing

During a time when the semi-conductor market is experiencing overwhelming demand for its products, there are a lot of cogs in the supply chain to ensure that everything is moving in the right direction as well as a growth in capacity across the board. Typically when the industry talks about supply constraints, it most often directed towards the ability to produce the silicon wafers and chips, however the post-production element of that is also important: being able to build this silicon into useable product for each market also needs to be scaled to meet demand, and this is also a point where we are seeing a squeeze in the industry.

Intel's current Rio Rancho campus

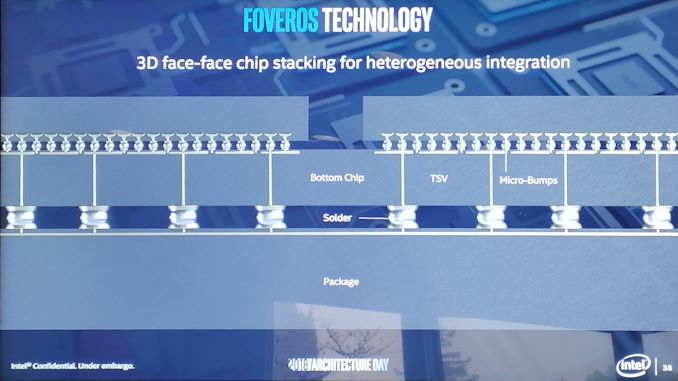

Today’s announcement of $3.5 billion USD for an expanded Intel facility in Rio Rancho is along those lines. This expanded facility won’t be building silicon wafers or silicon chips, but instead will be taking chips that are already made (made either at Intel or other foundries like TSMC) and constructing them into a package which is then sold onto partners. This facility will be specializing in construction using Intel’s new 3D packaging technology, also known as Foveros, as well as continuing investments in Intel’s Embedded Multi-Die Interconnect Bridge (EMIB) technology.

Foveros is a die-to-die packaging technology that connects two chips together. Intel has already enabled Foveros on one technology in the market, a laptop processor called Lakefield, as well as a product currently in production, the high-performance compute processors called Ponte Vecchio, set to be used in the Aurora supercomputer as one of America’s largest computing projects to date. So far these two projects are specialized, with comparatively few units compared to Intel’s major product lines. With the expanded facility at Rio Rancho, Intel intends to invest in its capability to roll out products co-designed with its advanced packaging technologies like Foveros on a wider scale.

CEO Pat Gelsinger with a Ponte Vecchio XPU using EMIB+Foveros

Construction for the new expansion is set to start in late 2021, and be production-ready by late 2022. Intel has confirmed to AnandTech that the facility is aimed purely at building its advanced 3D packaging and testing facilities for end products, rather than R&D into some of Intel’s other on-site activities, such as 3D XPoint, which had been postulated in the media.

We did ask Intel whether the new facility would be focused on 3D packaging solely for Intel’s own product lines, or whether it would be made available to Intel’s future Foundry customers as part of its Intel Foundry Services (IFS) program – Intel declined to comment, but stated that the facility will be managed by Keyvan Esfarjani, SVP and GM of Intel’s Manufacturing and Operations. Intel has also stated that it will purchase renewable energy to meet 100% of the electricity use at the expanded facility.

Intel’s press release on the news focuses specifically on Foveros deployment, however we are led to believe that EMIB production is also going to be bolstered by the expansion, given both fall under Intel’s advanced 3D packaging capabilities. Intel told us to consider this purely as a packaging and testing facility expansion, something that Intel already does a lot of, akin to what other companies might call an OSAT under their fabless models.

Related Reading

- Intel’s Future 7nm FPGAs To Use Foveros 3D Stacking

- Intel Next-Gen 10-micron Stacking: Going 3D Beyond Foveros

- An Interconnected Interview with Intel’s Ramune Nagisetty: A Future with Foveros

- Intel's Interconnected Future: Combining Chiplets, EMIB, and Foveros

- Intel’s New IDM 2.0 Strategy: $20b for Two Fabs

- What Products Use Intel 10nm? SuperFin and 10++ Demystified

20 Comments

View All Comments

nandnandnand - Monday, May 3, 2021 - link

https://www.tweaktown.com/news/78974/intel-in-nuts...https://www.tomshardware.com/news/intel-seeks-doll...

Intel is about to be handed billions in subsidies for new fabs. Is AMD getting anything or are they SOL for separating design and foundry?

bullzz - Monday, May 3, 2021 - link

Not just Intel. All chip manufactures are looking for subsidies. AMD doesn't get squatYojimbo - Monday, May 3, 2021 - link

Why would AMD get anything? They are not a chip manufacturer.Morawka - Monday, May 3, 2021 - link

Plus AMD gave China keys to x86 and Zen 2 Arch, even though the US government told them not to. The USA needs lithography foundries to ensure national security. AMD shouldn't get subsidies if they aren't building fab capacity.sgeocla - Tuesday, May 4, 2021 - link

Stop spreading FUD. Intel tried to get into Chinese markets and made a joint venture with the Chinese company Spreadtrum to build x86 chips for Android devices in 2014, long before AMD's JV. So if anyone gave away x86 to the Chinese it was Intel. AMD only licensed Zen1 designs to their own JV and the dies were build on GF and only microcode was cusomised with Chinese encryption standards instead of US standards. Zen1 was considered to be an inferior design to the Intel designs so the US government did not consider it strategic. Zen2 was never a part of the JV deal.timecop1818 - Tuesday, May 4, 2021 - link

> Zen1 was considered to be an inferior design to the Intel designs so the US government did not consider it strategic.I mean, they're completely not wrong.

Spunjji - Tuesday, May 4, 2021 - link

Har-de-har. No, they weren't wrong.What's tragic for Intel fans is that AMD are now 3 design iterations on from Zen 1, while Intel only just replaced Zen 1's Skylake competition on desktop... with an inferior design. Oof.

Spunjji - Tuesday, May 4, 2021 - link

No, they didn't. This bullshit would be entirely irrelevant even if it were true.sgeocla - Wednesday, May 5, 2021 - link

It's completely true and very relevant. Intel entered the JV licensing deal with China first but people don't seem to remember because like a lot of other Intel ventures it completely failed, mostly due to 10nm being so late and unable to compete with TSMC. People need to stop reading WSJ payed for propaganda.Roy2002 - Monday, May 3, 2021 - link

Globalfroundries would get. AMD won't since it does not have fab.