Hot Chips 2020 Live Blog: Intel/Barefoot Tofino2 12.9 Tbps Switch (10:30am PT)

by Dr. Ian Cutress on August 18, 2020 1:30 PM EST- Posted in

- Networking

- Intel

- Bigfoot

- Switch

- Live Blog

- Ethernet

- Hot Chips 32

- Tofino2

01:27PM EDT - Live blog active! We're just a few minutes away from the Tofino2 presentation

01:27PM EDT - Intel acquired Barefoot last year, in a deal that closed in Q3

01:28PM EDT - From Intel's press release at the time:

01:28PM EDT - 'Barefoot Networks will add deep expertise [to Intel] in cloud network architectures, P4-programmable high-speed data paths, switch silicon development, P4 compilers, driver software, network telemetry and computational networking'

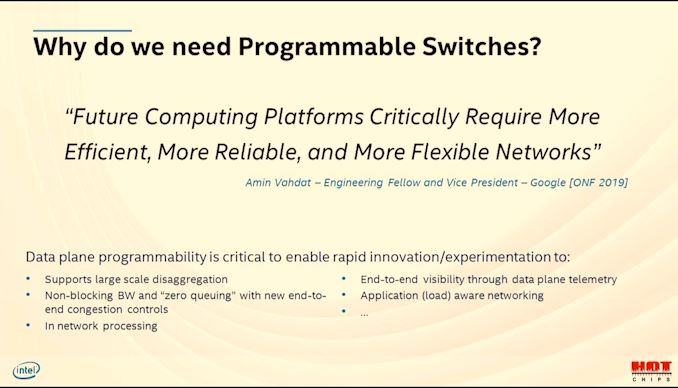

01:34PM EDT - 'Why do we need a programmable switch?'

01:34PM EDT - Future platforms need more reliable and flexible networks

01:35PM EDT - 2-3 cycle for switch silicon cycle is no longer sufficient

01:36PM EDT - Programmable switches are often considered 10-100x slower than fixed-function

01:36PM EDT - So need a paradigm shift in this thinking

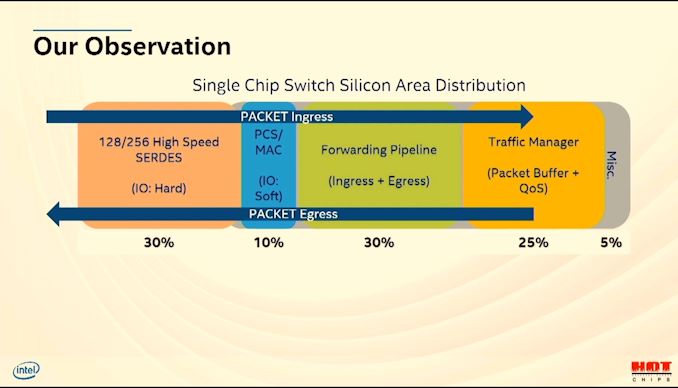

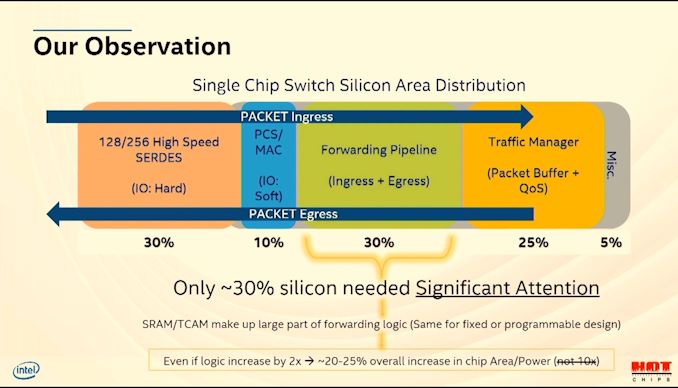

01:36PM EDT - This is where the power is managed in switch silicon

01:37PM EDT - Only the 30% in green needs attention - the rest is very fixed function

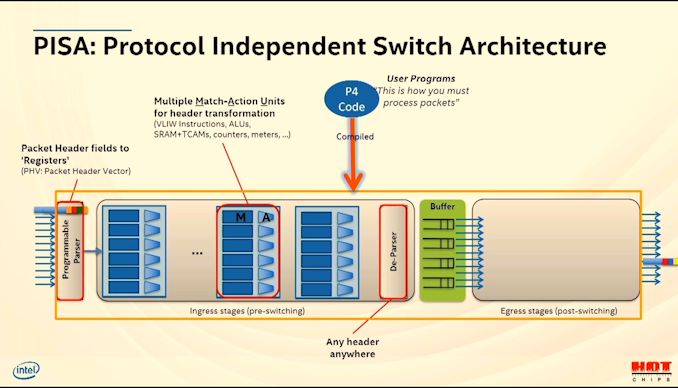

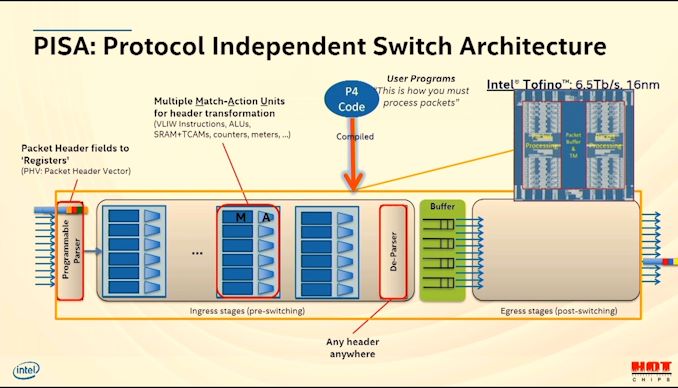

01:37PM EDT - Took the traditional feed-forward architecture of fixed function and made it all programmable

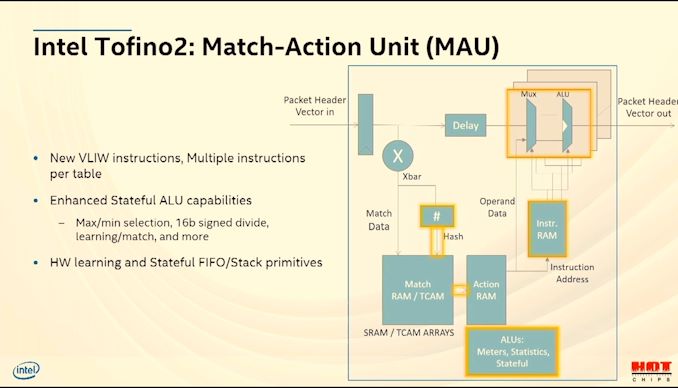

01:38PM EDT - Multiple Match Action Units - VLIW, ALU, SRAM

01:38PM EDT - New PISA architecture - protocol independent switch architecture

01:38PM EDT - Custom forwarding logic can be precompiled and applied to the switch

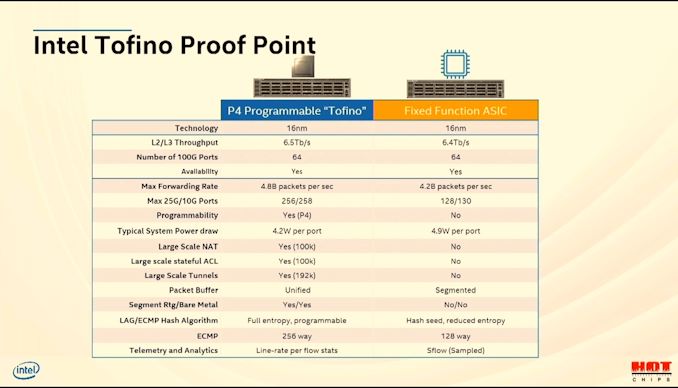

01:39PM EDT - This produced Tofino in 16nm, 6.5 Tb/s

01:39PM EDT - Tofino was better than competitor fixed function silicon

01:39PM EDT - Can this be repeated and scaled?

01:40PM EDT - Introducing Tofino2

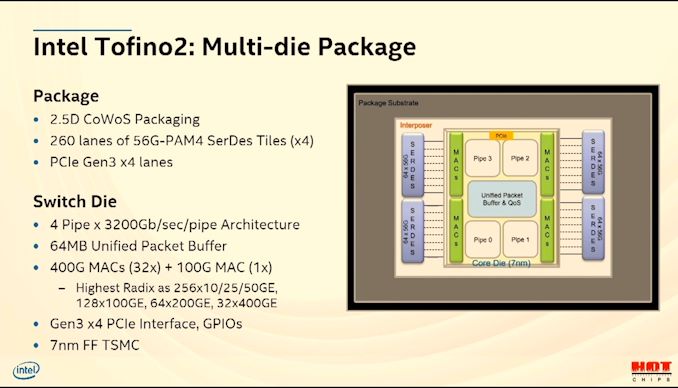

01:40PM EDT - Doubled down the programmability - double the capability

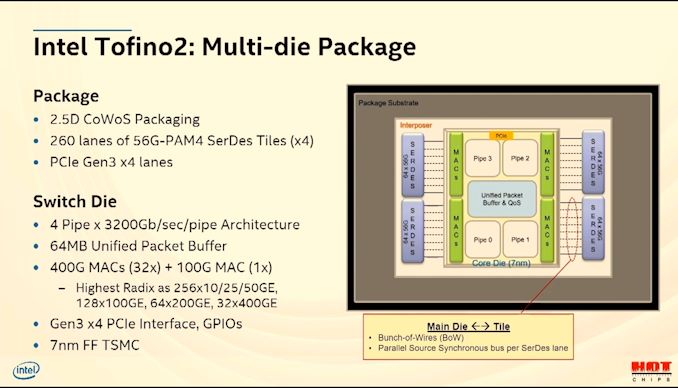

01:40PM EDT - Built on TSMC 7nm

01:40PM EDT - 6 billion packets/sec, 12.9 Tb/s

01:40PM EDT - Better QoS, better perf/watt

01:40PM EDT - PCIe 3.0 x4

01:41PM EDT - Multi-die package 2.5D CoWoS

01:41PM EDT - Custom BoW interdie interface

01:42PM EDT - (Surely next gen is EMIB then, if Barefoot is now Intel?)

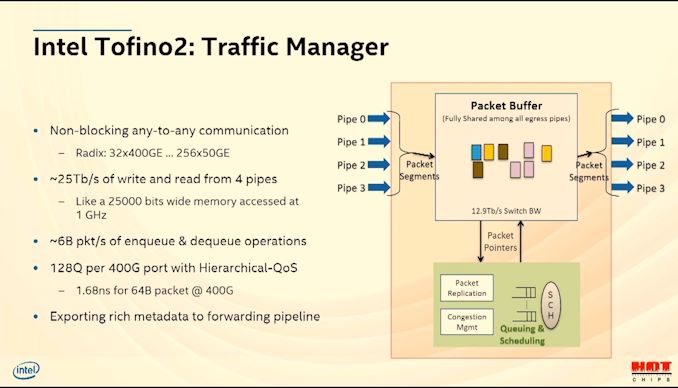

01:42PM EDT - Traffic Manager is like a 25000-bit wide memory accessed at 1 GHz

01:43PM EDT - Fully unified, fully flexible, non-blocking buffer

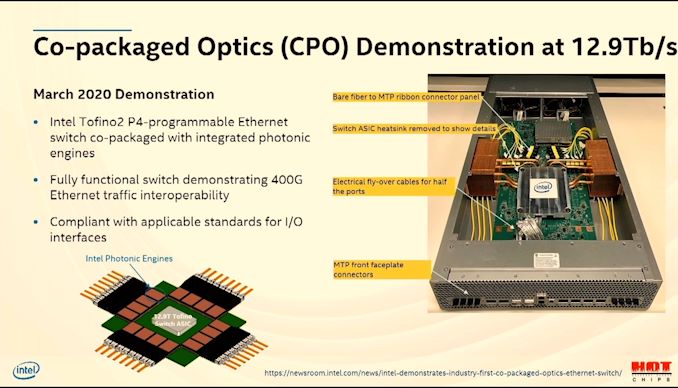

01:44PM EDT - Can be used with Silicon Photonics

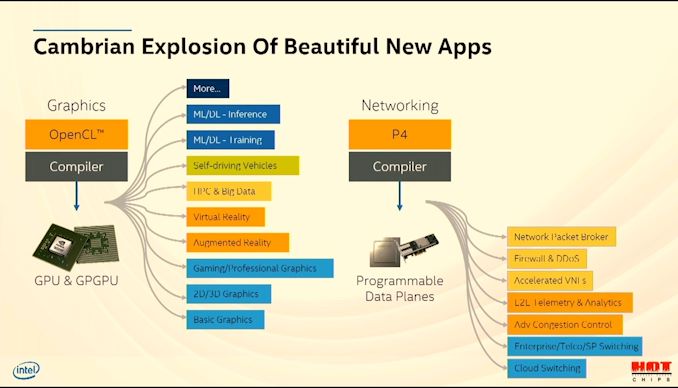

01:45PM EDT - With a programmable switch, the use case depends on the software

01:47PM EDT - (going through an animation as an example)

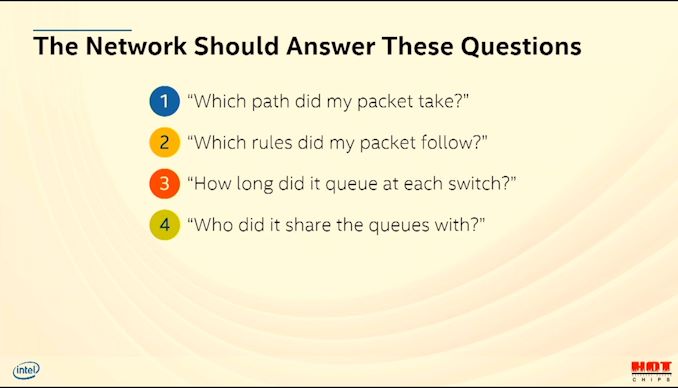

01:47PM EDT - Most switches don't enable the following questions to be answered

01:47PM EDT - This is the beauty of programmability

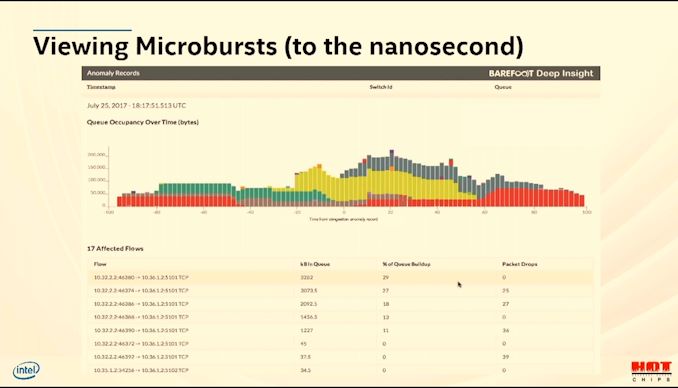

01:48PM EDT - Deep Insight software by Barefoot can do metrics on packet flow and adjust the programmability in the network as needed to ensure QoS

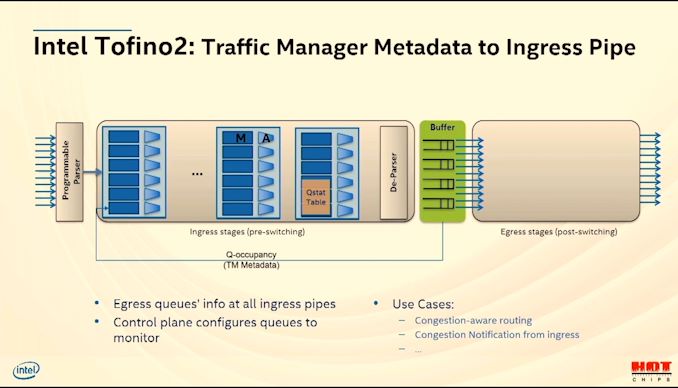

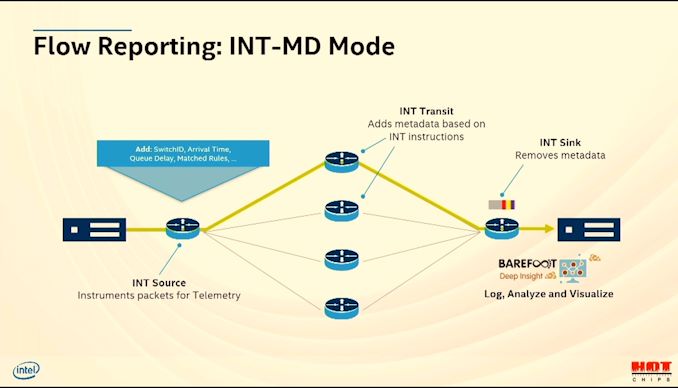

01:49PM EDT - Add metadata to a packet as the switch goes through switches, metadata stripped at last hop

01:49PM EDT - Maybe don't need to add info to every packet

01:49PM EDT - Need intelligent change detector

01:51PM EDT - Can see where the microcongestion is on the network

01:51PM EDT - Monitoring and control

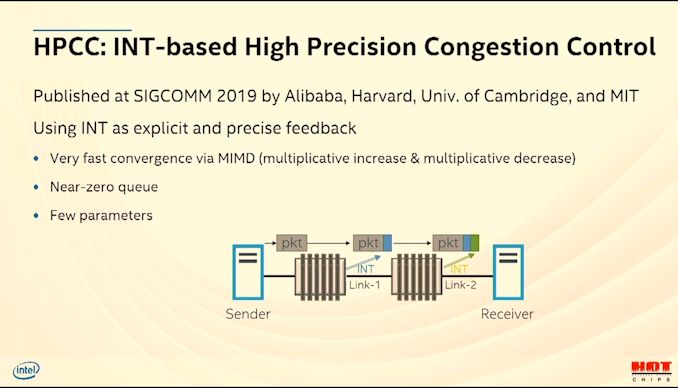

01:52PM EDT - This concept has already been showcased by Alibaba

01:52PM EDT - Lowers latency and flows completion time significantly

01:53PM EDT - Also application-based acceleration for networking

01:54PM EDT - Such as DNN

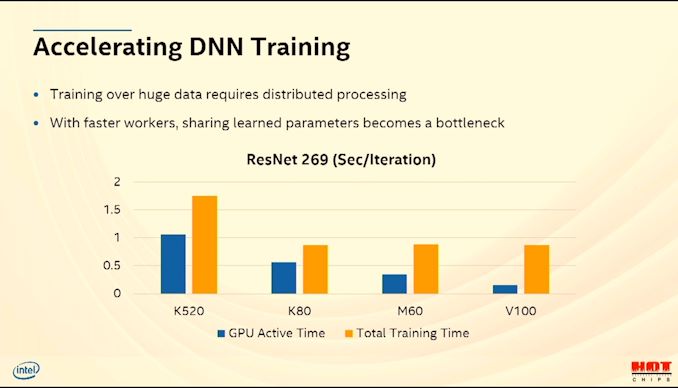

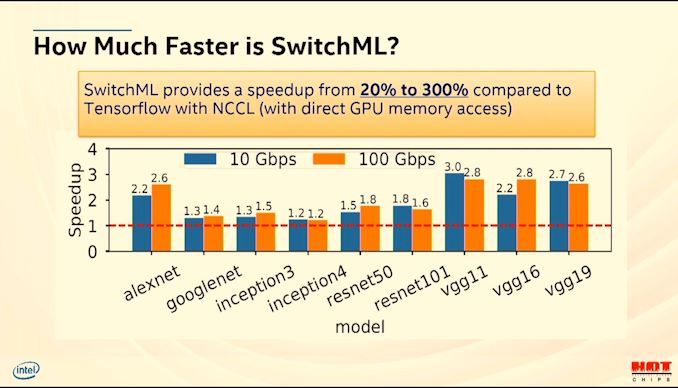

01:54PM EDT - Total time to train involves compute + network traffic - network traffic is not insignificant

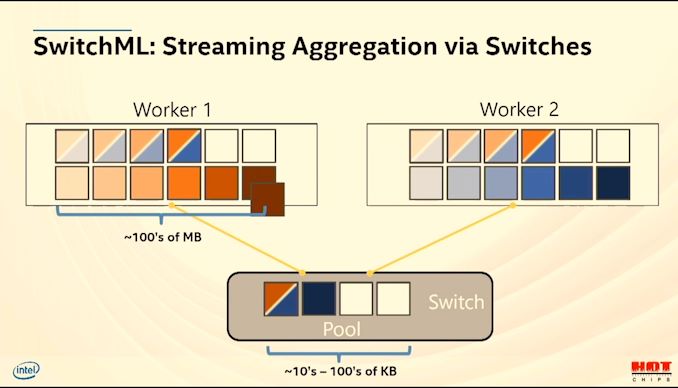

01:55PM EDT - Can use switches for streaming aggregation

01:55PM EDT - Can share between switch and SmartNIC

01:56PM EDT - Q&A time

02:00PM EDT - Q: Non-Ethernet support? 400 Gb/s or 800 Gb/s ? A: The design with Ethernet MAC on die, so only talks to ethernet right now. But as the chip is programmable, it doesn't tie to Ethernet L2 hierarchy, so as long as you have the stack, it will wack. Tofino2 supports 400G

02:02PM EDT - Q: Where's the time source? A: Latency from hub doesn't require time from switch. Each switch will do entry/exit latency, which will add over the chain. In datacenter you know the link, so it will be accurate. But PTP is possible

02:02PM EDT - Q: Compare to Mellanox SHARP? A: Similar, but we don't know much about Sharp. In general we're doing roughly the same thing, but in Tofino is implimented in P4 for easy customization

02:03PM EDT - Q: Die Size? A: Proprietary info

02:04PM EDT - That's a wrap. I'll be back at 1:30pm PT for the Keynote

1 Comments

View All Comments

JayNor - Tuesday, August 18, 2020 - link

ok, we don't need the xilinx slide.