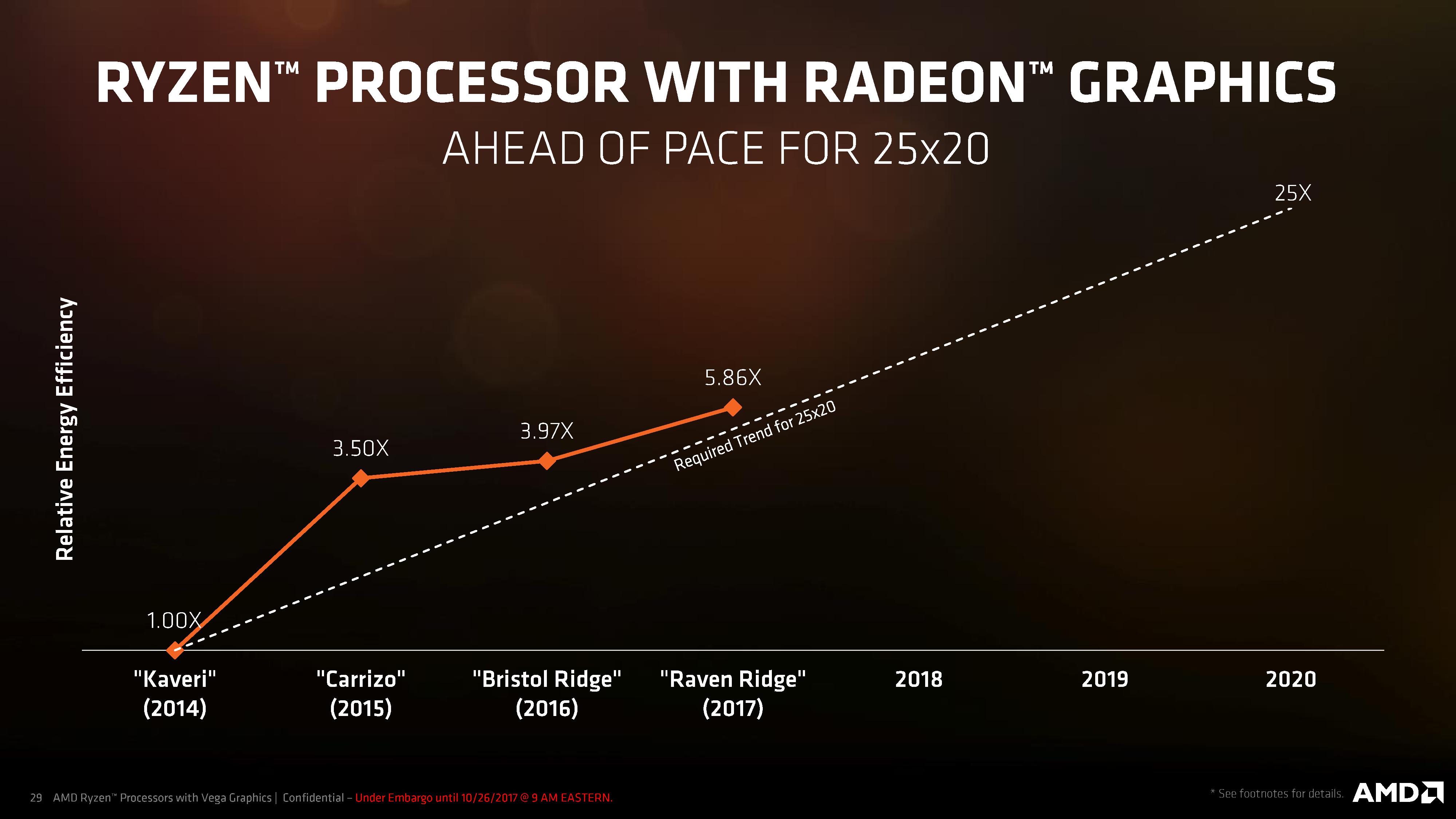

AMD's Progress on Its 25x20 Goal: The Task Ahead

by Ian Cutress on October 26, 2017 9:05 AM EST

When AMD announced it was creating the new high-performance Zen core, they set a lofty goal. They wanted to produce products that offered 25x the relative efficiency (performance per watt) between 2014 and 2020. This was called the 25x20 goal, and AMD gave an update.

Starting from a baseline of Kaveri, AMD has put the Ryzen Mobile processors currently at 5.86x the performance efficiency in 3 years. That leaves another ~5x performance to get in the next three years. That’s a steep hill to climb, and it is clear that the scale of the graph above seems to be wrong, with Ryzen Mobile being half-way up the graph, rather than around 20% up the graph. If AMD is set to make that target, then they are expecting a huge jump in efficiency coming up. Is that what Navi is?

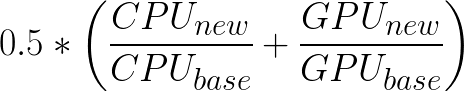

For this data, AMD also gave some insight into how they are calculating it. In the footnotes, we get the following steps:

- Overall performance efficiency is C divided by E

- Performance is a 50:50 average of CPU and GPU performance (variable ‘C’) compared to Kaveri

- CPU Performance from Cinebench 15 Multi-Threaded

- GPU Performance from 3DMark 11 P - Energy Use (variable ‘E’) defined by ETEC ‘Typical Energy Consumption from Notebooks’ as per Energy Star Program Requirements Rev 6.1 Oct-2014

- Kaveri is the Baseline where C/E = 1.00x

To calculate C, the following equation is used:

So say for example the base processor scored 100 in Cinebench and 1000 in 3DMark 11. If the upgraded processor scored 150 and 2000, the overall value of C would be 0.5 x (150/100 + 2000/1000) = 1.75.

To calculate C, we have to go to the Energy Star documents and pull out this long equation:

The PT(x) options are the power consumed in those modes multiplied by a given weighting factor in the document listed above. But it is worth noting that because it involves system level power in off/sleep/idle states, it is also subject to any efficiency improvements from the other component manufacturers as well, such as DRAM, IO, power delivery and display. Part of the goal here is performed by the vendors, not AMD.

AMD provided all the benchmark data for the CPU and GPU parts, as well as ‘overall’ values for E. These are all taken from mobile APU parts.

| AMD's 25x20 Goal: Progress | |||||

| Cinebench R15 nT |

3DMark 11 P | Variable C | Variable E | Performance Efficiency |

|

| Raven Ridge | 719 | 4315 | 2.56 | 0.44 | 5.86x |

| Bristol Ridge | 279 | 3234 | 1.36 | 0.34 | 3.97x |

| Carrizo | 277 | 2709 | 1.23 | 0.35 | 3.51x |

| Kaveri | 232 | 2142 | 1.00 | 1.00 | 1.00x |

From the table, we can clearly see that moving from Kaveri to Carrizo was mainly about the power consumption under the Energy Star test, moving the denominator to a nice low number. Moving from Carrizo to Bristol Ridge was about GPU performance, extracting the most out of the 28nm process for frequency at the same power and some better binning. The jump to Raven Ridge/Ryzen Mobile marks a big step for Cinebench, given the new high-performance core, and a bump in 3D Mark performance.

What is interesting to note is that the variable ‘E’ has gone up from Bristol Ridge to Raven Ridge, from 0.34 to 0.44. This is despite AMD claiming a 58% power reduction in workloads like Cinebench. This will be down to how the Energy Star guidelines are set out, which in this instance do not favor how a system is applying the power (regardless of performance).

It brings up how AMD is going to achieve its 25x goal by 2020. Ryan and I discussed this at length before I wrote this segment, but there are a few interesting things to note.

Calculating E: It's in the System

In order to calculate E, AMD relies on a good representation of the whole system, not just the processor. That includes things like memory, the display, and other components. This means that the improvements in these segments should help significantly towards that goal. One major thing that AMD could do with the next generation is swap support for DDR4 to either LPDDR3 or LPDDR4. The reason why is the low power states.

When we asked why AMD is not supporting LPDDR memory on Ryzen Mobile, the response was related to performance. If we look at almost every single Intel 15W notebook on the market, despite the processors supporting both LPDDR3 and DDR4, they all use LPDDR3 by default. If we ask the OEMs, the answer lies in the power consumption during lower power modes such as idle: LPDDR memory can achieve much, much lower power modes than standard DDR. We put this to AMD and they looked confused, saying that literally none of their OEM partners had ever brought this up in conversation as a requirement for a future platform.

Nonetheless, that value of E could take a nice tumble when AMD implement LPDDR on a future APU. I’d bet some money on that being the case.

Process Nodes Matter

Ryan also pointed out that AMD could implement a super low power SKU, something like Intel’s Core-M line that sits at 4.5W. At that low power, the value for E should be cut considerably. However, we have to think if these parts actually have a lower idle/off power than Intel’s 15W, or if it is, in fact, all in the binning. They would certainly have lower VRM losses by having fewer VRMs in play anyway. This is something AMD could pursue, assuming the performance values could be kept high.

We are also expecting AMD to implement GlobalFoundries 7nm process before 2020. That should yield a number of improvements for power, especially if AMD decides to fab a chip on a low power node.

The Future of Performance

On the C side of the equation, more is better. There are still a couple of iterations in the public roadmap for Zen from now until 2020, so the CPU performance could increase another 10-25%. Moving to 7nm could also lend itself to doubling the core count, giving a sizeable increase in the Cinebench or 3DMark score. With extra transistors and new GPU architectures (like Navi, or beyond), there is room to grow.

We did some mockup numbers to see where AMD would sit. The new 25x20 table would look like this based on three potential scenarios.

| AMD's 25x20 Goal: Future? | |||||

| Cinebench R15 nT |

3DMark 11 P | Variable C | Variable E | Performance Efficiency |

|

| Same Power | 2000 | 18000 | 8.51 | 0.34 | 25.04x |

| Half Power | 1000 | 8000 | 4.02 | 0.16 | 25.14x |

| Low Power | 800 | 4400 | 2.75 | 0.11 | 25.01x |

| Raven Ridge | 719 | 4315 | 2.56 | 0.44 | 5.86x |

| Bristol Ridge | 279 | 3234 | 1.36 | 0.34 | 3.97x |

| Carrizo | 277 | 2709 | 1.23 | 0.35 | 3.51x |

| Kaveri | 232 | 2142 | 1.00 | 1.00 | 1.00x |

In the same power scenario (0.34E, like Bristol Ridge), AMD would have to severely increase both CPU performance by 3x and GPU performance by over 4x. An obvious way to go in that direction would be to double everything, although that is not always an easy task when it requires keeping power the same, even over several generations. A crystal ball will predict 8-core laptops, though it will be interesting to see the power, the frequencies, and the process node.

For a half-power scenario (0.16E), we took the fact that AMD is likely to increase its IPC over the next few generations by 5-15% each year. By 2020, assuming the same core count as today, this would give a Cinebench score of about 1000. In order to reach the 25x performance efficiency metric with that increase in CPU performance, the GPU would have to almost double in performance. One of the outcomes of moving to 7nm could be that AMD keeps the quad-core design but instead increases the number of compute units in the integrated GPU. Doubling the compute units, halving the power consumption, and increasing IPC by 30% is a tall order in three years, even with a node change and new architectures.

Ryan’s preferred option is the low power scenario. If AMD created a 4.5W-like processor which overall reduced the variable ‘E’ by ~75%, along with the general system improvements like LPDDR, but kept about the same performance as the 15W chips of today, then AMD could hit the 25x metric fairly comfortably. This might be considered an easier task than the others, and it will depend on how AMD is able to manage the power with such a low ceiling.

This is where I put in a poll to see what people think of where AMD will sit come 2020:

How will AMD achieve its 25x20 goal? See https://t.co/ghOwCn8E1C for details

— Ian Cutress (@IanCutress) October 26, 2017

I have set the poll to last for 7 days. The results should speak for themselves.

20 Comments

View All Comments

junky77 - Thursday, October 26, 2017 - link

The twitter poll shortcode doesn't workMajGenRelativity - Thursday, October 26, 2017 - link

Well, higher efficiency is always good. It's interesting to see where AMD will go.jonnyFlash - Thursday, October 26, 2017 - link

The graph is in log-scale, such that the improvement from 1 to 5 (5 fold) has equal distance as the improvement from 5 to 25 (5 fold). Its the only scale that makes sense.ABR - Thursday, October 26, 2017 - link

Yeah, not sure why the author just gets through saying "they've done 5x, and they've got another 5x to go", then says the graph looks wrong for showing halfway?! Another 5x *from here* will do it.peevee - Thursday, October 26, 2017 - link

There is no way they reduce power by 4x (0.44/0.11) while keeping the same or better performance.BrokenCrayons - Thursday, October 26, 2017 - link

Why not? Look at the difference between a mobile Pentium 4 and a mobile Kaby Lake CPU in power consumption for a given unit of compute performance. The trouble for AMD in improvement is more the number of years remaining until they have to deliver. As long as the production process can be improved, AMD's 25x20 goal isn't totally unreasonable, but even if it doesn't happen by 2020, there'll be some point in the future where we're enjoying 25x more performance per watt than we were in 2014. Competitive market forces make that pretty much inevitable.iwod - Thursday, October 26, 2017 - link

Because you are comparing two extreme situation. Pentium 4 was never designed with with minimal power consumption in mind, in fact it was quite the opposite, Ghz = Power. And its node was also not for Mobile usage. While Kaby is designed with Mobile CPU in mind along with Low Power node.BrokenCrayons - Thursday, October 26, 2017 - link

Then compare a Core 2 Duo with a Kaby Lake CPU if it bothers you that much or use a Cyrix Media GXm. Whatever floats your nitpicky boat is fine with me. I'm not interested in having a nerd slap-and-hair-pull fight with someone that wants to argue against reality for the sake of being absurdly stubborn.Kamen75 - Thursday, October 26, 2017 - link

Yep 25x is definitely possible before the end of 2020. If they covered 5.86x in the first three years then that leaves another 4.27x to put them past their 25x goal over the next 3 years. So, 12nm LPP for 2018, 7nm for 2019, and 7nm+ in 2020 plus architectural improvements should do it.lefty2 - Thursday, October 26, 2017 - link

LPDDR3 isn't a clear win over DDR4.LPDDR3 draws several times less power in idle than DDR4, however DDR4 draws 20% less power when active. This image from Samsung shows this: http://i.imgur.com/AVjraML.png.